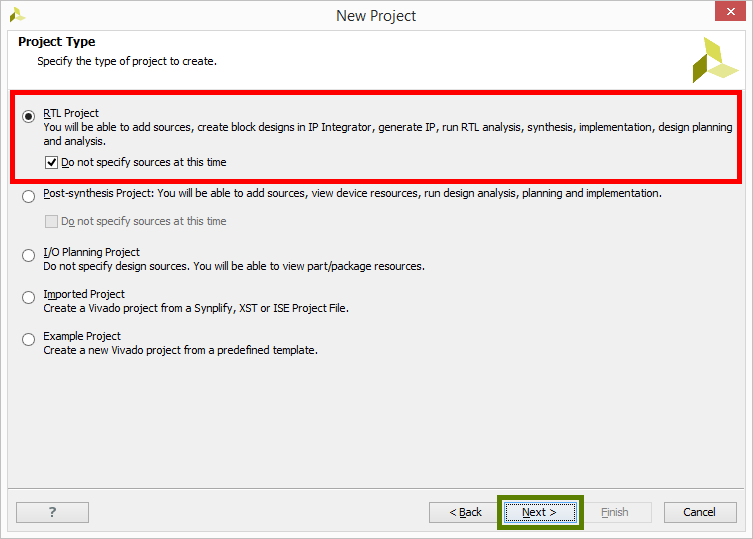

Click OK in the Add Constraints File. Compile the design in the Quartus II software.This file has the appropriate constraints needed for this Vivado project. If you have not already done so, create a new project or open an existing project.

Add A Vivado Project To Synplify Pro Verification Of Semiconductors

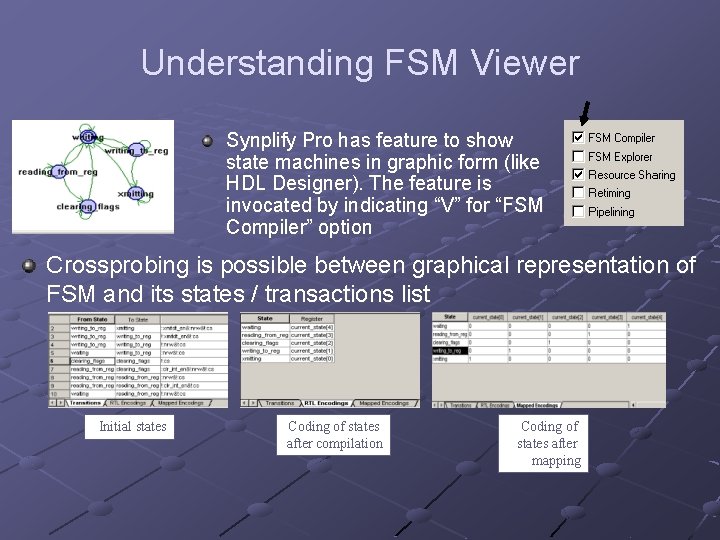

Synplicity® also announced the Synplify Pro software supports the Xilinx Modular Design Flow. Additionally, the new release offers support for IP cores whose timing is modeled in the STAMP format, enabling improved timing performance in designs using pre-synthesized IP. With this new release, the synthesis product includes support for FPGA designs containing both Verilog and VHDL modules, known as ``mixed-language'' designs. (Nasdaq: SYNP), a leading supplier of software for the design and verification of semiconductors for Internet infrastructure, today announced it has enhanced its Synplify Pro(TM) synthesis solution to support designers integrating intellectual property (IP) into high-density FPGAs. 13, 2000- Synplicity, Inc.

Pricing for the Synplify software starts at $9,000 (U.S.) and pricing for Synplify Pro software starts at $19,000 (U.S.). Additionally, the Synplify synthesis solutions now offer support for Actel 54SXS and eX families, Lattice SuperFAST and SuperWIDE families, Lucent Orca4 family and QuickLogic QuickDSP family.The Synplify 6.1 and Synplify Pro 6.1 synthesis solutions are available now. Together these improvements provide APEX users with significantly faster performing devices.Support for New Devices from Leading VendorsFor the first time, the Synplify products include support for Triscend's A7 and E5 device families, which offer a configurable SoC solution to address high-performance, customizable SoC applications. This approach is important for the design of very complex devices where portions of the design must be completed incrementally.This new release of Synplify software includes several new quality of results improvements for Altera's APEX20K and APEX20KE family of devices including automatic inference of Up/Down counters, improvements for timing optimization, mapping of cascade/carry chains, automatic inferencing or ROMs and mapping to LPM ROMs and NativeLink support for Unix. Using the Synplify Pro product within the Modular Design Flow, design teams can easily define modular boundaries for each team member, and generate separate netlists and constraints for each section of the design. With this release, sequential shift components are automatically inferred and then implemented as an SRL (Shift Register Lookup) table, significantly improving performance in designs using these components.For the first time, the Synplify Pro software includes support for the Xilinx Modular Design Flow.

...

0 kommentar(er)

0 kommentar(er)